Hynix 32GB DDR5 Registered Memory — HMCG84AGBRA192N

Premium server-grade RAM from SK Hynix: a 32GB DDR5 RDIMM designed for enterprise servers,

workstations and high-performance computing. Optimized for stability, low-voltage efficiency and

error-correcting reliability.

Manufacturer & Part Information

Vendor Details

- Manufacturer: SK Hynix

- Part Number (MPN): HMCG84AGBRA192N

- Product Name: 32GB DDR5 SDRAM Registered RDIMM

- Product Category: Memory module / server RAM

Detailed Technical Specifications

Memory & Electrical

- Memory Technology: DDR5 SDRAM (Double Data Rate 5).

- Module Size: 32GB (1 x 32GB module).

- Bus Speed: 5600 MT/s — labeled DDR5-5600 / PC5-44800.

- Operating Voltage: 1.1V (low-voltage DDR5 specification).

Performance & Organization

- CAS Latency: CL46 timing for balanced latency vs throughput.

- Rank: Single rank (1R) — 1Rx4 configuration.

- ECC: Error-correcting code supported (server-grade reliability).

- Registration: Registered (buffered) DIMM for improved signal integrity.

- Pin Count: 288-pin RDIMM physical interface.

Top Features & Benefits

- Capacity: 32GB single module — ideal for memory expansion and heavy workloads.

- Speed: 5600 MT/s (DDR5-5600 / PC5-44800) for faster data throughput.

- Error Correction: ECC (error-correcting code) to protect data integrity.

- Registered / Buffered: RDIMM format improves signal stability in multi-module systems.

- Low Voltage: Operates at 1.1V for better energy efficiency compared with older generations.

- Latency: CL46 timing tuned for DDR5 performance.

- Form Factor: 288-pin DIMM compatible with servers and select workstations.

Compatibility & Use Cases

- Enterprise servers and database hosts.

- Virtualized environments and hypervisors.

- High-performance computing (HPC) and rendering farms.

- Mission-critical applications that require ECC and registered memory.

- Requires motherboards and server platforms that support DDR5 RDIMM modules.

- Check vendor compatibility lists for supported SK Hynix part numbers and firmware revisions.

- Mixing different speeds or types (UDIMM vs RDIMM) is not recommended — use matched modules for best stability.

Hynix HMCG84AGBRA192N 32GB DDR5 RDIMM

Understanding DDR5 Server Memory Technology

The Evolution from DDR4 to DDR5 Architecture

The transition from DDR4 to DDR5 represents one of the most significant advancements in memory technology in recent years. DDR5 memory modules, such as the Hynix HMCG84AGBRA192N, deliver substantial improvements in performance, power efficiency, and reliability compared to their DDR4 predecessors. With data rates starting at 4800MT/s and scaling beyond 5600MT/s, DDR5 provides nearly double the bandwidth of equivalent DDR4 modules while operating at lower voltages.

Key Architectural Changes in DDR5

DDR5 introduces several fundamental architectural changes that differentiate it from previous generations. The most notable innovation is the implementation of two independent 40-bit data channels (32 data bits with 8 ECC bits) per module, effectively doubling the burst length to 16 while maintaining the same BL8 operation per channel. This dual-channel architecture on a single DIMM allows for significantly improved concurrent access patterns and reduces latency in memory-intensive applications.

Power Management Integration

DDR5 modules incorporate a revolutionary approach to power management by moving the power management IC (PMIC) from the motherboard to the memory module itself. This architectural shift enables more precise voltage regulation and better power distribution, resulting in improved signal integrity and stability. The PMIC allows for granular power control and enhances the module's ability to handle power spikes and fluctuations, which is critical in enterprise environments where system stability is paramount.

Hynix HMCG84AGBRA192N Module Specifications

Performance Characteristics

The Hynix HMCG84AGBRA192N operates at a data rate of 5600 megabits per second (MT/s), which translates to an effective speed of 5600MHz. With a module organization of 2G x8 using x4 DRAM architecture, this 32GB RDIMM delivers exceptional bandwidth of PC5-44800, providing ample performance for data-intensive enterprise applications. The module's CAS latency of 46 cycles represents an optimized balance between speed and stability for server environments.

Timing Parameters Breakdown

The timing configuration of the HMCG84AGBRA192N follows the JEDEC standard for DDR5-5600 modules with CL46 timing. The complete timing parameters include tRCD (Row Address to Column Address Delay) and tRP (Row Precharge Time) typically set to 46 cycles, with tRAS (Row Active Time) configured for optimal performance. These carefully calibrated timings ensure reliable operation while maximizing data throughput in enterprise server configurations.

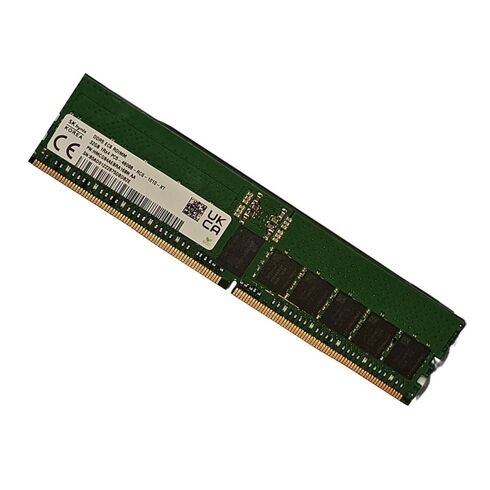

Physical and Electrical Characteristics

This DDR5 RDIMM utilizes a standard 288-pin design with a unique notch position that prevents incorrect installation in incompatible slots. The module operates at a nominal voltage of 1.1V, representing a significant reduction from DDR4's 1.2V operation, contributing to improved power efficiency in data center environments. The reduced operating voltage directly translates to lower power consumption and reduced heat generation, critical factors in high-density server deployments.

Thermal and Mechanical Design

The Hynix HMCG84AGBRA192N features a standard server RDIMM profile with optional thermal sensors for temperature monitoring. The mechanical design ensures proper airflow across the module surface in server chassis configurations, while the PCB construction provides optimal signal integrity at high data rates. The module's construction meets enterprise reliability standards with rigorous testing for vibration, shock, and long-term operational stability.

ECC and Registered DDR5 Technology Explained

Error Correcting Code (ECC) Implementation

On-Die ECC Architecture

The Hynix HMCG84AGBRA192N incorporates sophisticated Error Correcting Code capabilities that represent a significant evolution from previous ECC implementations. DDR5 ECC operates with two distinct layers: traditional sideband ECC that protects data in transit between the memory controller and DRAM, and innovative on-die ECC that corrects errors within the DRAM chips themselves before data leaves the memory device. This dual-layer approach substantially improves reliability and reduces uncorrectable error rates.

Error Detection and Correction Capabilities

The ECC implementation in this DDR5 RDIMM can detect and correct single-bit errors automatically, while also detecting multi-bit errors within the same ECC word. The module utilizes a sophisticated algorithm that can correct any single symbol error (4-bit nibble) and detect any two symbol errors within a 64-byte data block. This advanced error correction capability is essential for mission-critical applications where data integrity cannot be compromised.

Registered DIMM (RDIMM) Architecture

Buffer Chip Functionality

As a Registered DDR5 DIMM, the HMCG84AGBRA192N incorporates a Registering Clock Driver (RCD) that buffers command, address, and clock signals between the memory controller and the DRAM chips. This buffering reduces the electrical load on the memory controller, enabling support for higher module densities and more DIMMs per channel. The RCD in DDR5 RDIMMs has been enhanced to support the higher data rates and improved signal integrity requirements of the DDR5 specification.

Benefits of Registered Architecture in Server Environments

The registered architecture provides several critical advantages in enterprise server configurations. By reducing the electrical load on the memory controller, RDIMMs enable more stable operation with higher numbers of modules per channel and support for greater total memory capacity. This makes registered DDR5 modules ideal for servers requiring large memory configurations, such as database servers, virtualization hosts, and high-performance computing applications where maximum memory capacity and stability are essential.

Long-Term Reliability Features

Signal Integrity Enhancements

DDR5 technology incorporates several enhancements to improve signal integrity and long-term reliability. The Hynix HMCG84AGBRA192N implements Decision Feedback Equalization (DFE) in the data receivers, which helps compensate for channel losses and inter-symbol interference at high data rates. This sophisticated signal processing capability enables reliable operation at 5600MT/s while maintaining timing margins that ensure data integrity over the module's operational lifetime.

Extended Operational Lifespan

The HMCG84AGBRA192N is engineered for extended operational life in demanding 24/7 server environments. The module's components are selected and qualified for continuous operation at elevated temperatures typical of server conditions. With robust PCB design, high-quality materials, and comprehensive testing, Hynix DDR5 RDIMMs provide the durability necessary for mission-critical applications where memory reliability directly impacts business operations and service delivery.

Comparative Analysis with Alternative Technologies

DDR5 RDIMM vs. Other Memory Form Factors

Within the DDR5 ecosystem, the Hynix HMCG84AGBRA192N as an RDIMM must be understood in context with other available form factors. Compared to Unbuffered DIMMs (UDIMMs), RDIMMs offer greater capacity and stability in multi-DIMM configurations but with slightly higher latency due to the registering process. Load Reduced DIMMs (LRDIMMs) provide even greater capacity potential but at higher cost and power consumption. The RDIMM represents the optimal balance for most enterprise applications.

DDR5 in Relation to Emerging Memory Technologies

While DDR5 represents the current mainstream standard for server memory, it exists alongside emerging technologies such as Compute Express Link (CXL) which enables memory expansion and pooling. In the foreseeable future, DDR5 will continue to serve as the primary main memory technology, with CXL and other technologies complementing rather than replacing DDR5 for most server workloads. The Hynix HMCG84AGBRA192N provides a solid foundation for current server platforms while maintaining compatibility with future technological developments.